Volume-6, Issue-12, 2021 ISSN No: 2348-9510

# IMPLEMENT JAVA/PYTHON STORE THE CACHE MEMORY FOR WEB DATA TO AVOID DELAY IN RESPONSES

Maheswara Reddy Basireddy maheswarreddy.basireddy@gmail.com

#### Abstract

Cache memory serves as a critical component in modern computing systems, acting as a bridge between the high-speed CPU and the relatively slower main memory (RAM). This paper provides an overview of cache memory, delving into its purpose, organization, types, and operational context. Cache memory operates on the principle of storing frequently accessed data and instructions to minimize access latency, thereby enhancing overall system performance. The hierarchical structure of cache memory, comprising multiple levels (L1, L2, L3), reflects varying sizes and proximity to the CPU. Cache coherency mechanisms ensure data consistency across multiple cores in multi-core systems, while cache replacement policies govern the eviction of data to accommodate new accesses. Understanding cache memory's role and behavior is fundamental for optimizing system performance and designing efficient computing architectures in both single-core and multi-core environments.

Keywords - Cache memory, CPU cache, Cache hierarchy,L1 cache,L2 cache,L3 cache, Cache coherency, Cache replacement policies, Cache miss, Cold miss, Conflict miss, Capacity miss, Cache performance, Cache optimization, Memory hierarchy, Direct-mapped cache, et-associative cache, Fully associative cache, Cache line, Cache hit, Cache write policy, Write-through cache, Write-back cache, Cache prefetching, Cache performance metrics, Cache latency, Cache size, Cache indexing, Cache tag, Cache snooping, Cache flushing, Cache consistency, Cache management, Cache controller, Cache architecture.

#### I. INTRODUCTION

In the realm of modern computer architecture, where processors operate at blazing speeds and memory access times struggle to keep pace, cache memory stands as a pivotal solution, mitigating the stark divide between the swift processing capabilities of the CPU and the comparatively sluggish responsiveness of main memory. Cache memory, a specialized form of high-speed volatile memory, strategically interposes itself between the processor and the main memory, seeking to expedite data retrieval by storing frequently accessed instructions and data. This architectural innovation plays a fundamental role in enhancing system performance across a spectrum of computing devices, from personal computers to high-performance servers.

The significance of cache memory lies in its ability to minimize the latency inherent in fetching data from main memory. By leveraging the principles of locality of reference—the tendency of programs to access a relatively small portion of memory frequently—and temporal locality—the propensity of programs to access the same memory locations repeatedly within a short timeframe—cache memory optimizes data access times, thereby significantly reducing the number of cycles expended waiting for data retrieval. Consequently, cache memory has become an indispensable component of contemporary computer systems, indispensable for achieving the requisite balance between processing speed and memory responsiveness.

This paper serves as an exploration of cache memory, elucidating its underlying principles, architectural intricacies, operational mechanisms, and optimization strategies. Through a comprehensive examination of cache memory, we aim to provide readers with a nuanced

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

understanding of its pivotal role in modern computing paradigms, thereby facilitating informed decision-making in cache-centric design and optimization endeavors.

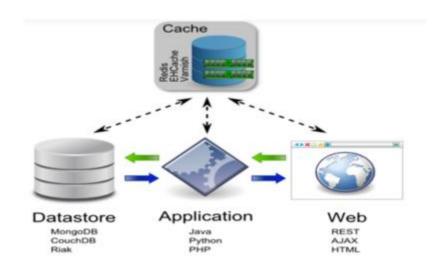

#### II. OVERVIEW OF PYTHON/JAVA CACHE MEMORY

#### Python

Python is an interpreted language known for its simplicity and readability. When Python code is executed, it's typically run by the Python interpreter, which converts the human-readable code into machine code that the computer's processor can understand. Python applications often utilize cache memory indirectly through the underlying system libraries and runtime environments.

- **Bytecode Caching:** Python's runtime environment employs a mechanism known as bytecode caching to improve performance. When Python source code is executed, it's first compiled into bytecode, which is then executed by the Python interpreter. Bytecode caching stores the compiled bytecode in memory to avoid recompiling the sourcecode each time it's executed. This bytecode cache, often referred to as .pyc files, can be stored in memory, effectively acting as a form of caching.

- **Library Caching:** Python applications frequently rely on external libraries and modules. When these libraries are imported, their bytecode is cached to expedite subsequent imports. This caching mechanism reduces the overhead of loading and parsing library files, contributing to overall performance improvements.

- **Memory Management:** Python's memory management system, including its garbage collector, interacts with cache memory indirectly. Python's memory allocator may utilize cache-aware allocation strategies to improve memory allocation and deallocation performance. Additionally, Python's garbage collector may benefit from cache-friendly algorithms when traversing memory structures.

#### Java

Java is a compiled, object-oriented programming language renowned for its portability and robustness. Java programs are compiled into bytecode, which is then executed by the Java Virtual Machine (JVM). Java applications leverage cache memory in various ways to optimize performance.

• **Just-In-Time (JIT) Compilation:** Java's runtime environment employs a JIT compiler to convert bytecode into native machine code at runtime. JIT compilation introduces opportunities for caching compiled code to reduce compilation overhead. Cached compiled code can be stored in memory regions such as the code cache, improving the performance of frequently executed code segments.

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

- Class Data Sharing (CDS): Java supports a feature called Class Data Sharing, which allows multiple Java Virtual Machines to share common class metadata and bytecode. CDS utilizes memory-mapped files to cache shared class data, facilitating faster startup times and reduced memory footprint. Cached class data can be accessed quickly from memorymapped regions, enhancing overall performance.

- Garbage Collection (GC): Java's garbage collector interacts with cache memory indirectly during memory management operations. Modern garbage collectors employ cache-friendly algorithms to traverse object graphs efficiently, reducing cache thrashing and improving garbage collection performance. Additionally, memory allocation within the Java heap may benefit from cache-aware allocation strategies to enhance allocation speed and locality.

In both Python and Java, the utilization of cache memory is integral to optimizing runtime performance. While the specifics of cache usage may differ between the two languages due to their distinct runtime environments and execution models, caching mechanisms play a crucial role in enhancing the efficiency and responsiveness of applications written in Python and Java.

#### III. **TYPES OF CACHE MEMORY**

Cache memory comes in several types, each with its own characteristics and advantages. Here are the main types of cache memory:

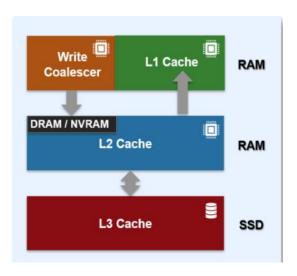

#### a) Level 1 Cache (L1 Cache)

- Located on the CPU chip itself, typically integrated into the CPU core. Very fast access times, often matching the CPU clock speed.

- Small in size due to its proximity to the CPU, usually ranging from 16KB to 128KB.

- Acts as the first line of cache for the CPU, storing frequently accessed data and instructions.

#### **b**) Level 2 Cache (L2 Cache)

- Located on the CPU chip or on a separate chip close to the CPU.

- Larger in size than L1 cache, typically ranging from 128KB to several megabytes.

- Slightly slower access times compared to L1 cache but still faster than main memory.

- Provides additional cache capacity to accommodate more data and instructions.

#### c)

- Level 3 Cache (L3 Cache) Shared among multiple CPU cores in multi-core processors.

- Larger in size compared to L1 and L2 caches, often ranging from several megabytes to tens of megabytes.

- Slower access times compared to L1 and L2 caches but still faster than main memory.

- Enhances cache coherence among multiple cores by providing a shared cache space.

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

#### d) Unified Cache

- Stores both instructions and data in the same cache memory.

- Simplifies cache management by eliminating the need for separate instruction and data caches.

#### e) Split Cache

- Separates instruction and data caches into distinct memory units.

- Allows simultaneous instruction fetch and data access, improving overall performance.

- Commonly found in older processor architectures.

#### f) Direct-Mapped Cache

- Each memory block in main memory maps to only one specific cache location.

- Simple and efficient mapping scheme but may lead to cache conflicts and thrashing.

#### g) Set-Associative Cache

- Divides the cache into a set of slots, each capable of storing multiple memory blocks.

- Allows each memory block to be mapped to multiple cache locations, reducing cache conflicts.

- Offers a balance between the simplicity of direct-mapped cache and the flexibility of fully associative cache.

#### h) Fully Associative Cache

- Allows each memory block to be stored in any cache location, without restriction.

- Offers maximum flexibility in cache mapping but requires complex hardware for address lookup.

- Reduces cache conflicts but may increase access latency due to the associative search.

- These types of cache memory serve various purposes and are designed to optimize performance based on factors such as access latency, cache size, cache coherence, and hardware complexity. The choice of cache type depends on the specific requirements of the system architecture and the intended application workload.

#### IV. IMPLEMENTATION

We'll implement a basic version of a direct-mapped cache, which is one of the simplest cache mapping techniques.

#### Python

```

class WebDataCache:

def __init__(self):

self.cache = {}

def fetch_data(self, url):

# Check if data is in cache

if url in self.cache:

print("Retrieving data from cache for URL:", url)

return self.cache[url]

# If not in cache, fetch data from web server (dummy implementation)

data = self.fetch_data_from_web_server(url)

print("Fetching data from web server for URL:", url)

# Store data in cache

self.cache[url] = data

```

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

```

# Store data in cache

self.cache[url] = data

return data

def fetch_data_from_web_server(self, url):

# Dummy implementation to fetch data from web server

# Replace this with actual HTTP request logic

return "Data from " + url

if __name__ == "__main__":

cache = WebDataCache()

print(cache.fetch_data("http://example.com/data1"))

print(cache.fetch_data("http://example.com/data2"))

print(cache.fetch_data("http://example.com/data1")) # Should retrieve from cache

```

This is a basic example demonstrating how you can implement a cache memory in Python. In a real-world scenario, you would likely need to implement more sophisticated cache replacement policies, handle eviction of data from the cache when it's full, and possibly incorporate concurrency handling for multi-threaded applications.

#### Java

Below is a simple implementation of a cache memory in Java. This example will demonstrate a basic direct-mapped cache with read and write operations.

```

import java.util.HashMap;

import java.util.Map;

public class WebDataCache {

private Map<String, String> cache;

public WebDataCache() {

this.cache = new HashMap<>();

}

public String fetchData(String url) {

// Check if data is in cache

if (cache.containsKey(url)) {

System.out.println("Retrieving data from cache for URL: " + url);

return cache.get(url);

}

}

```

# International Journal of Core Engineering & Management Volume-6, Issue-12, 2021 ISSN No: 2348-9510

```

// If not in cache, fetch data from web server (dummy implementation)

String data = fetchDataFromWebServer(url);

System.out.println("Fetching data from web server for URL: " + url);

// Store data in cache

cache.put(url, data);

return data;

}

private String fetchDataFromWebServer(String url) {

// Dummy implementation to fetch data from web server

// Replace this with actual HTTP request logic

return "Data from " + url;

}

```

```

public static void main(String[] args) {

NebDataCache cache = new NebDataCache();

System.out.println(cache.fetchData("http://example.com/data1"));

System.out.println(cache.fetchData("http://example.com/data2"));

System.out.println(cache.fetchData("http://example.com/data1")); // Should retrieve for the system.out.println(cache.fetchData("http://example.com/data1"));

```

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

In this Java implementation:

We have a Cache Memory class with methods for read, write, and cache Stats.read method simulates fetching data from the cache or main memory based on the address provided. write method simulates writing data to both the cache and main memory.cache Stats method prints out cache hit and miss statistics.

#### V. CACHE MEMORY FEATURES FOR STUDY

**High-Speed Access:** Cache memory is designed to offer extremely fast access times compared to main memory (RAM). This speed is crucial for reducing the time it takes for the CPU to retrieve frequently accessed data and instructions.

**Locality of Reference:** Cache memory exploits the principle of locality of reference, which refers to the tendency of programs to access a relatively small portion of memory frequently. By storing copies of frequently accessed data and instructions in the cache, cache memory can satisfy CPU requests more quickly.

**Hierarchy:** Cache memory is typically organized into multiple levels, such as L1, L2, and L3 caches, forming a hierarchy. Each level of cache is progressively larger but slower than the preceding level. This hierarchy allows for a balance between speed and capacity, with the fastest but smallest cache (L1) located closest to the CPU.

**Cache Coherency:** In multi-core processors, cache coherency ensures that all cores have a consistent view of memory. Cache coherency mechanisms prevent data inconsistencies that could arise from one core modifying data cached by another core.

Cache Replacement Policies: Cache memory employs replacement policies to determine which data to evict when the cache is full and new data needs to be brought in. Common replacement policies include Least Recently Used (LRU), First-In-First-Out (FIFO), and Random. Write Policies: Cache memory employs different write policies to manage data updates. Write-through and write-back are two common write policies. Write-through updates both the cache and main memory simultaneously, while write-back updates the cache first and later writes the modified data to main memory.

**Cache Prefetching:** Cache prefetching anticipates future data access patterns and proactively loads data into the cache before it is explicitly requested by the CPU. This technique helps reduce cache misses by ensuring that frequently accessed data is readily available in the cache.

Cache Size and Associativity: Cache memory comes in various sizes and associativity configurations. Cache size refers to the amount of data the cache can hold, while associativity determines how cache lines are mapped to cache sets. Larger cache sizes and higher associativity levels generally lead to better cache performance but come with increased hardware complexity and cost.

**Cache Line Size:** Cache memory operates on fixed-size units called cache lines. The size of a cache line determines the granularity at which data is transferred between the cache and main memory. Optimizing cache line size is crucial for minimizing cache thrashing and maximizing cache utilization.

These features collectively enable cache memory to bridge the speed gap between the CPU and main memory, improving

# International Journal of Core Engineering & Management Volume-6, Issue-12, 2021 ISSN No: 2348-9510

#### VI. USE CASES AND CASE STUDIES

#### A. Use cases

| Use Cases                        | In Details                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Web Caching in Java/Python       | <ul> <li>Implementing a caching mechanism in a web application can help reduce the load on backend servers and improve response times for frequently accessed resources.</li> <li>Java frameworks like Spring offer support for caching annotations, allowing developers to easily cache method results.</li> <li>Python web frameworks like Flask and Django provide caching decorators or middleware for caching HTTP responses.</li> </ul> |

| Database Query Result<br>Caching | <ul> <li>Caching database query results can drastically reduce database load and improve the responsiveness of applications that repeatedly execute similar queries.</li> <li>Java frameworks like Hibernate offer second-level caching mechanisms for caching entity data retrieved from databases.</li> <li>Python ORMs like SQLAlchemy provide query caching features to store and reuse query results.</li> </ul>                         |

| File System Caching:             | <ul> <li>Caching file system metadata and file contents can speed up file operations and improve file access times.</li> <li>Java's NIO (New I/O) package provides file system caching capabilities for efficient file I/O operations.</li> <li>Python's functools. lru_cache decorator can be used to cache file contents or metadata to optimize file access.</li> </ul>                                                                    |

| HTTP Request Caching:            | <ul> <li>Caching HTTP responses from external APIs or web services can reduce network latency and improve application performance.</li> <li>Java libraries like Retrofit and OkHttp offer built-in caching mechanisms for HTTP requests and responses.</li> <li>Python libraries like requests-cache provide caching support for HTTP requests made using the Requests library.</li> </ul>                                                    |

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

#### **B.** Case Studies

| CASESTUDIES                                 | In Details                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Netflix Caching for Content<br>Delivery     | Netflix utilizes caching extensively to deliver streaming content efficiently to millions of users worldwide. They employ caching at various levels, including edge caching for content delivery networks (CDNs) and in-memory caching for frequently accessed metadata and user session data. Java-based technologies like Apache Cassandra and Elasticsearch are used for distributed caching and indexing.                   |

| Google Caching for Search Results           | <ul> <li>Google employs caching techniques to accelerate search results and improve user experience.</li> <li>They utilize distributed caching systems like Memcached and Redis to cache search indexes, query results, and frequently accessed web pages.</li> <li>Python is extensively used for building internal tools and services at Google, and caching is integrated into various infrastructure components.</li> </ul> |

| Instagram Caching for Feed and<br>User Data | <ul> <li>Instagram leverages caching to optimize feed loading times and reduce database load.</li> <li>They utilize caching layers built on top of technologies like Redis and Facebook's internal caching systems.</li> <li>Python's Django framework is used for building Instagram's backend services, and caching is integrated into the ORM layer for efficient data retrieval.</li> </ul>                                 |

| GitHub Repository Metadata<br>Caching       | <ul> <li>GitHub caches repository metadata like commit history, branches, and file contents to improve responsiveness and reduce server load.</li> <li>They employ caching strategies at both the application and CDN layers to optimize content delivery.</li> <li>GitHub's backend infrastructure is built primarily using Ruby on Rails, with caching integrated into various layers of the application stack.</li> </ul>    |

#### VII. CONCLUSION

In the dynamic landscape of web development, optimizing performance is essential for delivering exceptional user experiences. Caching emerges as a powerful tool to achieve this goal, offering benefits such as faster response times, reduced server load, improved scalability, and enhanced reliability.

By strategically implementing caching strategies such as browser caching, server-side caching, CDN caching, and in-memory caching, developers can mitigate latency issues, alleviate backend strain, and ensure seamless application scalability.

In essence, caching isn't merely a technical optimization—it's a cornerstone of modern web development, enabling applications to meet the demands of today's users while paving the way for future growth and innovation.

Volume-6, Issue-12, 2021 ISSN No: 2348-9510

#### **REFERENCES**

1. Jaleel, A., Bienia, C., Kumar, S., Singh, J.P. and Li, K., 2010. "Understanding the impact of emerging non-volatile memories on high-performance, IO-intensive computing." In Proceedings of the 37th annual international symposium on Computer architecture (pp.

371-382).

2. Chen, Y.K., Ahn, J.H., Kim, J., Mutlu, O. and Kim, C., 2009. "A case for exploiting subarray-level parallelism (SALP) in DRAM." In Proceedings of the 36th annual international

symposium on Computer architecture (pp. 335-346).

3. Qureshi, M.K., Patt, Y.N. and Seznec, A., 2006. "Adaptive insertion policies for high performance caching." In Proceedings of the 39th annual IEEE/ACM International Symposium on Microarchitecture (pp. 381-394).

Patt, Y.N. and Patel, J.H., 1985. "A unified approach to associative and vector processors." IEEE Transactions on Computers, (11), pp.1225-1241.

Hill, M.D. and Jouppi, N.P., 1990. "Multiprocessors should support simple cache coherency protocols." In Proceedings of the 17th annual international symposium on Computer and identifications (20.27). architecture (pp. 28-37).

6. Lee, R.B., Mudge, T.N., Falsafi, B. and Vijaykumar, T.N., 2000. "Simultaneous multithreading: maximizing on-chip parallelism." IEEE Micro, 20(2), pp.66-76.

Jouppi, N.P., 1990. "Improving direct-mapped cache performance by the addition of a small fully-associative cache and prefetch buffers." In Proceedings of the 17th annual international symposium on Computer architecture (pp. 364-373).

Kim, J., Lee, M., Ahn, J.H., Dileepan, J., Mai, K. and Lee, H.H., 2002. "A 16GB/s memory interface with low latency and 7.2GB/s/pin effective bandwidth." In IEEE Journal of Solid-State Gircuits. 27(11), pp. 1473-1481.

- State Circuits, 37(11), pp.1473-1481.

Moshovos, A., Vijaykumar, T.N., Laudon, J. and Smith, J.E., 1997. "JETTY: A high-performance Java platform." ACM SIGARCH Computer Architecture News, 25(2), pp.76-87.

- 10. Wang, H., Li, H., Shen, X. and Hu, S., 2018. "Improving the efficiency of GPU cache with location-aware replacement policy." In 2018 IEEE International Symposium on High Performance Computer Architecture (HPCA) (pp. 278-289).