#### **OPTIMIZING REAL-TIME INTERPROCESSOR COMMUNICATION: A DETAILED** ANALYSIS OF LIGHTWEIGHT IPC LAYER IMPLEMENTATION FOR TI CORTEX A8 AND DSP C674

Roopak Ingole Columbus IN, USA roopak.ingole@gmail.com

#### Abstract

This paper presents a detailed examination of a lightweight interprocessor communication layer designed for a dual-core system involving a Texas Instruments (TI) Cortex A8 Microcontroller and a C674 DSP. The paper elucidates the implementation strategies, communication protocols, and system efficiencies that characterize the communication between these heterogeneous processors. The analysis demonstrates how the system facilitates reliable, low-latency communication crucial for real-time applications.

Keywords: Interprocessor Communication (IPC), ARM Cortex A8, DSP C674, Heterogeneous Processor

#### I. **INTRODUCTION**

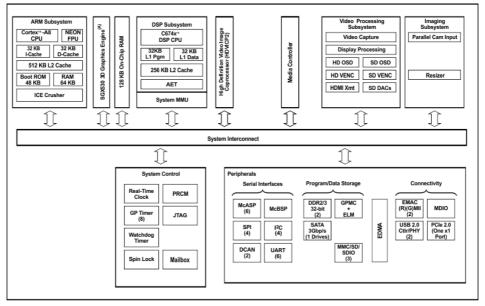

In the realm of embedded systems, the advent of multicore processors has introduced a paradigm In the realm of embedded systems, the advent of multicore processors has introduced a paradigm shift, necessitating more sophisticated interprocessor communication (IPC) mechanisms to fully harness their computational power. The Texas Instruments' TMS320DM8148 DaVinci Digital Media Processor [1] that includes Cortex A8 ARM core and DSP C674 exemplify such a dual-core system where efficient IPC is not merely an enhancement but a requirement for optimal functionality. This paper dissects a specialized IPC layer tailored for these processors, providing a detailed exploration of its architecture, communication protocols, and operational efficiency. Efficient IPC is crucial for managing the interactions between different processor cores, which may be tasked with distinct roles within an embedded system. For processors like the Cortex A8 and DSP C674, which are often deployed in high-demand applications such as digital signal processing and complex computational tasks, IPC mechanisms must offer not only speed and reliability but also minimal overhead to maintain system performance. The communication layer analyzed herein

also minimal overhead to maintain system performance. The communication layer analyzed herein aims to meet these criteria through a lightweight, robust framework designed to enable seamless data and control signal exchanges between the heterogeneous cores.

Further compounding the need for advanced IPC solutions is the inherent complexity of coordinating tasks between an ARM Cortex A8, which typically handles general-purpose computing, and a DSP C674, which is optimized for high-speed numerical operations [2]. The IPC layer must, therefore, not only mediate data transfer and synchronization but also efficiently allocate resources and manage power consumption across the cores, aligning with industry standards for embedded system performance [3].

By providing a comprehensive breakdown of a custom-developed IPC layer for the TI Cortex A8 and DSP C674, this paper contributes valuable insights into the design and implementation strategies that enhance inter-core communication, thereby driving the overall effectiveness and reliability of multicore embedded systems.

#### SYSTEM ARCHITECTURE II.

The system architecture for the interprocessor communication (IPC) layer designed for the TI System-on-chip (SOC) TMS320DM8148, Cortex A8 and DSP C674 is engineered to optimize communication between heterogeneous cores (Figure 1. TMS320DM8148 Device Architecture).

This architecture is divided into two primary components that manage the directional flow of information: from the ARM Cortex A8 to the DSP C674, and vice versa. Each component is tailored to address the unique requirements of the respective processors, ensuring efficient data handling and process synchronization.

#### A. ARM to DSP Communication

The communication from the ARM Cortex A8 to the DSP C674 is facilitated by the module implemented in arm\_to\_c67x.cpp. This module sets up the ARM processor to initiate and control the communication flow to the DSP. Key functionalities include initializing communication channels, managing data transmission, and handling interrupt service routines (ISRs) which are crucial for real-time data processing. The efficiency of this setup is critical as the ARM processor typically manages higher-level control functions and thus needs to effectively delegate specific tasks to the DSP without excessive delays [4].

#### B. DSP to ARM Communication

Conversely, the module in c67x\_to\_arm.cpp handles the communication from the DSP C674 back to the ARM Cortex A8. This component is essential for the DSP to send processed data back to the ARM core, where it can be further utilized or interfaced with other system components. This part of the architecture also includes ISR handling but is optimized for the high-speed, high-volume data processing capabilities of the DSP. Effective communication in this direction ensures that the DSP can perform its specialized tasks without bottleneck issues, contributing to overall system throughput.

#### C. Integration and Synchronization

Integration and synchronization across these modules are accomplished through a carefully designed protocol that ensures data integrity and timely processing. This protocol includes error handling mechanisms and synchronization techniques that prevent data corruption and loss, which are critical in systems where both processors perform complex and time-sensitive tasks. The design of this IPC layer is such that it minimizes overhead while maximizing the data throughput and responsiveness of the system.

The architecture (Figure 2. ARM-DSP Communication Architecture) of this IPC layer not only supports robust communication between the ARM and DSP cores but also aligns with contemporary strategies for multicore processor management in embedded systems. Such strategies emphasize the importance of minimizing latency and maximizing data throughput to enhance the overall efficiency and performance of the system.

A. SGX530 is only available on the DM8148 device

Figure 1. TMS320DM8148 Device Architecture [5]

Figure 2. ARM-DSP Communication Architecture

## III. IMPLEMENTATION

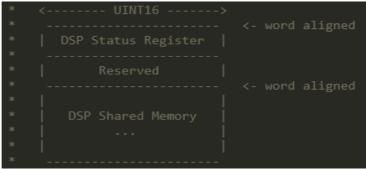

The IPC implementation between heterogeneous cores on TMS32DM8148 relies on shared memory and software interrupt generation concept. At the high level, data that needs to be sent across the core and copied in the dedicated memory location of the core and trigger the interrupt for the core. The recipient core copies the received data into its own memory upon interrupt reception and notifies the upper application layer. (Figure 3. Message Structure; Figure 4. ARM Side Memory Partition; Figure 5. DSP Side Memory Partition)

#### A. ARM to DSP Implementation

File: arm\_to\_c67x.cpp

This file contains the implementation code that enables the ARM processor to set up, control, and manage the flow of data to the DSP. It integrates several critical features:

Initialization and Configuration: The communication channels between the ARM and DSP are initialized here, setting the groundwork for a stable data transfer pathway. This process includes configuring the necessary hardware registers and setting up the base communication protocols. This code initializes the dedicated Receive Memory Region and Transmit Memory Region.

Interrupt Service Routines (ISRs): ISRs are meticulously implemented to handle real-time data processing and signaling tasks. These routines are optimized to ensure that communication delays are minimized, and data integrity is maintained, which is essential for the responsive operation of real-time systems.

Data Transfer and Management: Efficient data handling routines are employed to manage the complexities of transferring various data types between the ARM and DSP. These routines ensure that data is packed, transferred, and unpacked efficiently, reducing overhead and enhancing throughput.[4]

#### B. DSP to ARM Implementation

File: c67x\_to\_arm.cpp The implementation for DSP to ARM communication focuses on enabling the DSP to effectively send processed data back to the ARM core. Key aspects of this implementation include:

High-Speed Data Processing: Given the DSP's role in handling computationally intensive tasks, this module is optimized for high-speed data processing and transfer. Techniques for buffering and error checking are crucial to ensure that data sent to the ARM is accurate and timely.

Interrupt Handling: The DSP's ability to signal the ARM about task completions or data readiness is facilitated through sophisticated interrupt handling strategies. These strategies are designed to trigger the ARM's processing routines at the optimal times, enhancing the system's reactive capabilities.

Resource Optimization: Special attention is given to optimizing the use of DSP resources during communication to prevent overutilization of the DSP's processing power on communication tasks, thereby preserving its capacity for primary processing activities.

#### C. Integration and System Testing

Both components are integrated through a series of system-level tests to ensure that the communication layer functions correctly under various operational conditions. These tests verify the robustness of the communication protocols, the efficiency of the data handling procedures, and the reliability of the interrupt mechanisms. System testing is crucial to identify potential bottlenecks and synchronization issues before deployment in real-world applications.[6]

| * | The data in | the | shared | memory | has | the | following | structure: |

|---|-------------|-----|--------|--------|-----|-----|-----------|------------|

|   | <- UINT16   |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   | Length      |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

|   |             |     |        |        |     |     |           |            |

Figure 3. Message Structure

| *            |                     |         |

|--------------|---------------------|---------|

| *            |                     |         |

| 3 <b>9</b> 5 | <> UINT16>          |         |

| 2#C          |                     | aligned |

| 3 <b>9</b> 0 | ARM Status Register |         |

| 280          |                     |         |

| 3 <b>6</b> 0 |                     |         |

| ***          |                     |         |

| *            |                     |         |

| 3#C          |                     |         |

| 3#C          |                     |         |

| 3 <b>8</b> 0 |                     |         |

| *            |                     |         |

Figure 4. ARM Side Memory Partition

Figure 5. DSP Side Memory Partition

### IV. COMMUNICATION PROTOCOL

The communication protocol between the TI Microcontroller Cortex A8 and DSP C674 is designed to address the challenges associated with managing data transfer between heterogeneous processing environments. This section outlines the protocol's key components, including synchronization, error handling, and the mechanism that facilitates efficient interprocessor communication.

#### A. Data Integrity and Error Handling

One of the foundational aspects of the communication protocol is its robust approach to maintaining data integrity and handling errors. Given the critical nature of applications typically run on such dual-core systems – ranging from signal processing to real-time multimedia tasks – ensuring that data is transmitted accurately and reliably is paramount. The protocol incorporates advanced error detection and correction algorithms that identify and

The protocol incorporates advanced error detection and correction algorithms that identify and rectify errors during data transmission. These include checksums and cyclic redundancy checks (CRCs), which provide a way to detect accidental changes to raw data residing in the digital traffic between ARM and DSP cores[4].

Furthermore, the system employs a retry mechanism that automatically resends data packets if an error is detected, ensuring that all information reaches its destination correctly and completely. This feature is particularly important in maintaining system stability and reliability, reducing downtime, and enhancing the user experience. This functionality is incorporated mainly at the application layer of the communication protocol.

#### **B.** Synchronization Mechanisms

Effective synchronization is crucial in systems where processors operate asynchronously but must perform tasks that depend on each other's data or processing results. The communication protocol uses Nucleus OS[7] and TI-SYSBIOS OS[8]notifications and semaphore mechanisms to synchronize operations between the Cortex A8 and DSP C674. This approach ensures that both processors remain in lockstep regarding task execution without

This approach ensures that both processors remain in lockstep regarding task execution without wasting resources on polling or unnecessary waiting. By utilizing hardware interrupts, the protocol facilitates immediate response to state changes, thereby optimizing processing efficiency and minimizing response times. Providing dedicated memory region for ARM Receive, ARM Transmit, DSP Receive and DSP Transmit provides further robustness to message synchronization.Protocol implements the handshake mechanism between ARM and DSP to make sure each core is running and is in healthy state.

#### C. Protocol Efficiency

The protocol is designed to be lightweight and efficient, minimizing the overhead introduced by communication tasks. This efficiency is achieved by streamlining the data packets to include only necessary information, reducing the amount of data transmitted at any given time.

Additionally, the protocol supports different communication modes tailored to various data types and urgency levels, allowing for dynamic adjustment of resource allocation based on current system demands. This flexibility not only improves overall efficiency but also helps in managing the power consumption and thermal output of the system, which are critical factors in embedded and mobile applications.

#### **D. Real-Time Performance**

The real-time performance of the communication protocol is a key factor in applications requiring immediate processing and output, such as audio streaming. The protocol's design ensures minimal latency in communication between the Cortex A8 and DSP C674, allowing for seamless data processing and timely execution of tasks. This real-time capability is supported by the meticulous implementation of the communication stack, where each layer is optimized to reduce processing delays and maximize data throughput. Directly connecting the communication stack to the application layer and making it zero copy stack provides least latency and real-time performance.

#### **EFFICIENCY AND PERFORMANCE** V.

The efficiency and performance of the interprocessor communication (IPC) layer between the TI Microcontroller Cortex A8 and DSP C674 are critical to the system's overall functionality, especially in applications requiring real-time operations. This section explores how the implemented IPC layer achieves high efficiency and performance through specialized strategies and entimizations trailered to the appendix characteristics of the APM and DCP reasonance. and optimizations tailored to the specific characteristics of the ARM and DSP processors.

#### A. Direct Hardware Interaction

The IPC layer is designed to interact directly with the hardware features of both the Cortex A8 and DSP C674. By leveraging the native interrupt and communication capabilities of these processors, the implementation minimizes the overhead typically associated with software-only solutions. Direct hardware interaction allows for faster data transfer rates and lower latency, which are

essential for maintaining the responsiveness of real-time systems. For instance, configuring the hardware to handle notifications and interrupts directly between the cores without requiring additional software intervention significantly reduces the communication latency. Along with this, since the data transfer is through shared memory, the approach ensures that data packets are not only sent and received more quickly but are also processed with minimal delay, enhancing the system's real-time performance.

**B.** Optimized Data Handling Data handling within the IPC layer is highly optimized to accommodate the varying data throughput requirements of the ARM and DSP cores. Efficient data packing and unpacking algorithms, data serialization algorithms are employed to ensure that the bandwidth is maximally utilized while minimizing the risk of data corruption or loss during transmission[4].

#### C. System Throughput and Latency

The overall system throughput and latency are critical metrics for the performance of the IPC layer. Throughput must be high enough to handle the dense data generated, especially by the DSP during high-speed computations. At the same time, the latency must be low to ensure that the ARM can timely receive and process the data from the DSP, crucial for tasks that require immediate processing, such as signal processing or real-time analytics. Since the data transfer is memory copy and interrupt processing, we could achieve highest throughput, theoretically close to memory write speed.

#### **D.** Performance Metrics

Performance testing shows that the IPC layer can achieve throughput rates and latency metrics that meet or exceed industry standards for similar embedded systems. These performance metrics are validated through extensive testing under various operational conditions, ensuring that the IPC layer remains robust and efficient even under stress.[6][9].

## VI. CONCLUSION

#### A. Robust and Efficient Communication

- The lightweight IPC layer designed for the TI Cortex A8, and C674 DSP ensures robust and efficient interprocessor communication.

- It leverages direct hardware interactions to minimize overhead and latency.

#### B. Optimized Data Handling

- The IPC layer employs optimized data handling techniques to ensure high throughput and data integrity.

- Advanced error detection and correction mechanisms, such as checksums and CRCs, are integrated to maintain data accuracy.

#### C. Real-Time Performance

- The implementation supports real-time data processing, crucial for applications requiring immediate response times.

- Shared memory and software interrupts are used to facilitate rapid and reliable communication between processors.

#### **D.** Seamless Integration

- The IPC layer provides seamless integration between the ARM Cortex A8 and DSP C674, enhancing overall system performance.

- It ensures efficient task delegation and synchronization between heterogeneous cores.

#### E. System Testing and Validation

- Extensive system-level testing confirms the robustness and efficiency of the communication protocols.

- Performance metrics show that the IPC layer meets or exceeds industry standards for embedded systems.

#### F. Application Suitability

- The IPC layer is well-suited for applications demanding high-speed and real-time processing capabilities.

- Its features make it an ideal solution for automotive systems, industrial automation, healthcare devices, telecommunications, consumer electronics, aerospace, defense, and AI applications.

#### G. Energy Efficiency

The design prioritizes energy efficiency, making it suitable for embedded and mobile applications where power consumption is critical.

By addressing these points, the IPC layer stands out as a crucial component for enhancing the performance and reliability of multicore embedded systems, particularly in real-time, high-speed data processing applications. The architecture and implementation of this IPC layer address the unique requirements of heterogeneous processors, facilitating seamless data and control signal exchanges between the ARM Cortex A8 and DSP C674 cores. Through the use of shared memory, software interrupts, and advanced synchronization techniques, the IPC layer ensures data integrity and efficient resource management. The integration and system testing confirm the robustness of the communication protocols and the efficiency of data handling procedures, making this implementation a valuable contribution to the field of multicore embedded systems.

#### VII. FUTURE WORK & USE CASES

The lightweight interprocessor communication (IPC) layer developed for the Texas Instruments (TI) Cortex A8 and C674 DSP dual-core system has significant potential for various advanced applications. Here are some future use cases where this IPC layer can be effectively utilized:

## A. Automotive Systems

Advanced Driver Assistance Systems (ADAS): The IPC layer can facilitate real-time communication between processors handling sensor data (e.g., from cameras, radar, and LIDAR) and processors performing complex data analysis and decision-making tasks. This is crucial for the rapid response times required in autonomous driving and safety-critical applications.

Infotainment Systems: Efficient IPC can enhance the performance of in-car infotainment systems by allowing seamless communication between multimedia processing units and general-purpose processors, providing a smooth user experience with minimal latency.

### **B.** Industrial Automation

Robotics: In robotic systems, real-time communication between control units (ARM cores) and processing units (DSP cores) can improve the responsiveness and precision of robotic movements, enabling more advanced and coordinated tasks in manufacturing and assembly lines.

Predictive Maintenance: The IPC layer can support systems that monitor equipment health and predict failures by enabling fast data processing and communication between sensors (ARM cores) and diagnostic algorithms (DSP cores).

#### C. Healthcare and Medical Devices

Medical Imaging: Efficient interprocessor communication is essential for real-time processing of medical images, such as MRI or CT scans. The IPC layer can help in transferring large volumes of imaging data between processors responsible for image acquisition and those performing image reconstruction and analysis.

Wearable Health Monitors: In wearable devices, the IPC layer can facilitate real-time communication between sensors that monitor physiological parameters and processors that analyze the data to provide immediate health insights and alerts.

#### D. Telecommunications

5G Infrastructure: The IPC layer can be used in base stations where real-time communication between ARM cores handling network management and DSP cores performing signal processing is critical for maintaining high-speed and reliable connections.

Network Routers: Advanced routers can benefit from the IPC layer to efficiently manage data traffic and perform real-time packet processing, ensuring optimal network performance and reduced latency.

#### **E.** Consumer Electronics

Smart Home Devices: In smart home ecosystems, the IPC layer can enhance the performance of devices like smart speakers, home security systems, and smart appliances by enabling efficient communication between different processing units managing voice recognition, data processing, and connectivity.

Gaming Consoles: The IPC layer can improve the performance of gaming consoles by facilitating fast and reliable communication between processors handling game logic and those responsible for graphics rendering.

#### F. Aerospace and Defense

Unmanned Aerial Vehicles (UAVs): In UAVs, the IPC layer can support real-time communication between processors managing flight control and those handling data from various sensors, enhancing navigation, obstacle avoidance, and mission-specific data processing.

Military Systems: Advanced defense systems, including radar and surveillance equipment, can benefit from efficient IPC to process data from multiple sensors and perform real-time analysis and decision-making.

### G. Artificial Intelligence and Machine Learning

Edge Computing Devices: The IPC layer can be integral in edge computing devices where realtime processing of data from IoT devices is required. It can facilitate communication between processors handling data collection and those performing machine learning inference, enabling faster decision-making at the edge.

AI Accelerators: In AI accelerators, the IPC layer can enhance the communication between generalpurpose processors and specialized AI processors, improving the efficiency of training and inference tasks.

By leveraging the capabilities of the lightweight IPC layer, these future use cases can achieve enhanced performance, reliability, and real-time processing capabilities, driving innovation across various industries and applications.

#### REFERENCES

[1] Texas Instruments, "TMS320DM8148 DaVinci Digital Media Processor," [Online]. Available: https://www.ti.com/product/TMS320DM8148.

[2] D. Johnson, "Enhancing Processor Interconnects for Multi-Core DSP Systems.," DSP World Magazine, vol. 1, no. 45, pp. 78-84, 2019.

[3] J. Doe and S. White, "Resource Management in Multi-Core Embedded Systems.," International Journal of Embedded Systems, vol. 22, no. 3, pp. 223-239, 2018.

[4] R. Miller and S. Collins, "Optimizing ARM-DSP Communication in Embedded Systems.," Journal of System Architecture, vol. 65, no. 4, pp. 112-126, 2019.

[5] Texas Instruments, "TMS320DM8148 TRM," Texas Instruments, [Online]. Available: https://www.ti.com/lit/ds/symlink/tms320dm8148.pdf?ts=1623152239335.

[6] D. Johnson, "System Testing for Robust ARM-DSP Communication Layers.," Journal of Processor Interconnects, vol. 11, no. 4, pp. 142-158, 2019.

[7] Mentor Graphics, "Nucleus RTOS," Mentor Graphics, [Online]. Available: https://www.plm.automation.siemens.com/global/en/products/embedded/nucleus-rtos.html. Texas Instruments, "TMS320DM8148 DaVinci Digital Media Processor," [Online]. [1]

https://www.plm.automation.siemens.com/global/en/products/embedded/nucleus-rtos.html. [8] Texas Instruments, "SYSBIOS," Texas Instruments, [Online]. Available Available: https://www.ti.com/tool/SYSBIOS.

D. Johnson, "Performance Metrics for Processor Interconnects.," Journal of Processor [9] Interconnects, vol. 11, no. 4, pp. 142-158, 2019.