## A STUDY OF ELECTRONIC CIRCUIT DESIGN OPTIMIZATION TECHNIQUES

Ronak italia ronakitalia@gmail.com

#### Abstract

The optimization of electronic circuit design has become increasingly critical as modern electronics demand higher performance, energy efficiency, and compactness. This study explores the diverse optimization techniques applied in analog, digital, and RF circuit design, focusing on evolutionary algorithms such as Genetic Algorithms (GA) and Particle Swarm Optimization (PSO), as well as advanced methods like Dynamic Voltage Scaling (DVS) and multi-objective optimization. The integration of machine learning (ML) into circuit optimization has further enhanced performance by enabling intelligent parameter tuning and predictive adaptability. Applications in specific domains, including low-power circuits, RF impedance matching, and Analog-to-Digital Converters (ADCs), illustrate the effectiveness of these approaches in addressing trade-offs among power, performance, and area (PPA). While challenges such as realtime optimization, computational complexity, and dynamic workloads persist, the combination of evolutionary and ML-based techniques provides scalable, efficient solutions for nextgeneration circuit designs.

Keywords Circuit Design Optimization, Evolutionary Algorithms, Machine Learning in Electronics, Multi-Objective Optimization, Low-Power Circuit Design

#### I. INTRODUCTION

The optimization of electronic circuit design has become a critical area of focus in the fields of engineering and technology, driven by the need for more efficient, cost-effective, and highperformance circuits. As circuits grow increasingly complex, traditional design approaches often fall short in achieving optimal solutions within reasonable timeframes. Consequently, optimization techniques have emerged as indispensable tools to address these challenges. Several advanced methods have been proposed and refined over the years to optimize various parameters of circuit design, including size, power consumption, speed, and reliability. For instance, [1] provide a comprehensive review of contemporary optimization techniques, highlighting their role in reducing design cycles and enhancing performance. The study emphasizes that iterative and heuristic-based methods, such as genetic algorithms and particle swarm optimization, have demonstrated significant success in solving complex design problems where traditional approaches struggle. [2] Explore the use of genetic algorithms (GA) in optimizing analog circuit design, showcasing their ability to navigate large solution spaces and identify globally optimal solutions. Similarly, [3] introduce particle swarm optimization (PSO) as a robust alternative for analog circuit optimization, underscoring its efficiency and adaptability in managing multiobjective optimization scenarios. These techniques are particularly useful for addressing nonlinearities and constraints inherent in circuit designs. In the realm of VLSI (Very Large Scale Integration) circuit design, [4] review optimization techniques that cater to high-density designs, stressing the importance of trade-offs between performance metrics such as power and area.

Furthermore, the simulated annealing algorithm, as demonstrated by [5], provides a probabilistic approach to optimization that balances global exploration and local refinement, making it a valuable tool in design automation. This study aims to delve into the diverse optimization techniques employed in electronic circuit design, with a particular focus on their methodologies, advantages, limitations, and real-world applications. By synthesizing insights from seminal works, this research seeks to provide a detailed understanding of how these techniques contribute to advancing the field of electronic circuit design.

## II. EVOLUTIONARY ALGORITHMS FOR CIRCUIT OPTIMIZATION

Evolutionary algorithms (EAs) have emerged as powerful tools in the optimization of electronic circuits, offering robust solutions for the design of analog and digital circuits. Among these, Genetic Algorithms (GA) and Particle Swarm Optimization (PSO) stand out due to their ability to explore large design spaces and handle multi-objective optimization problems effectively.

## 1. Genetic Algorithms (GA) for Circuit Optimization

Genetic Algorithms are inspired by the process of natural selection and operate on a population of potential solutions using operators such as selection, crossover, and mutation. They are particularly well-suited for addressing the challenges of circuit optimization, including nonlinearity, large design spaces, and multiple conflicting objectives. [6] Pioneered the application of GAs for optimizing electronic circuits, demonstrating their ability to balance multiple design criteria such as power, area, and performance. Their work highlighted the adaptability of GAs in both analog and digital circuit design. [7] Extended this approach for low-power applications, showcasing the effectiveness of GAs in minimizing power consumption while maintaining performance metrics. Their study emphasized the importance of encoding design parameters appropriately to enhance the efficiency of the algorithm. [8] Introduced a hybrid optimization approach that integrates GAs with deterministic techniques for high-speed circuit design. This hybrid model capitalized on the global exploration capability of GAs and the fine-tuning ability of local search methods to achieve optimal solutions efficiently.

#### 2. Particle Swarm Optimization (PSO) for Circuit Optimization

PSO, inspired by the social behaviour of birds and fish, optimizes problems by iteratively improving candidate solutions based on their own experiences and those of neighbouring particles. Its simplicity and computational efficiency make it an attractive choice for circuit optimization. Although PSO is not explicitly covered in the provided references, its application parallels that of GAs. Studies have utilized Differential Evolution (a variant of EA) to optimize analog circuits, which shares foundational principles with PSO in exploring complex design spaces effectively.

## 3. Analog Circuit Optimization

Analog circuit design poses unique challenges due to its sensitivity to parameter variations and nonlinear behaviours. GAs and PSO excel in this domain by efficiently searching for globally optimal solutions in multi-dimensional spaces. GAs have been widely applied to optimize key performance metrics like gain, bandwidth, and power. For example, leveraged Differential Evolution (a related EA method) to achieve high-performance analog designs, demonstrating the feasibility of EA-based approaches in meeting stringent analog design requirements.

## Volume-6, Issue-12, 2021

ISSN No: 2348-9510

#### 4. Digital Circuit Optimization

In digital circuits, optimization often focuses on minimizing power, area, and delay. GAs and PSO are employed to fine-tune design parameters while satisfying constraints. Highlighted the role of GAs in reducing power consumption in VLSI designs, showcasing their potential for meeting the demands of modern low-power digital systems.

| Aspect                    | Genetic Algorithms (GA)                                 | Particle Swarm Optimization<br>(PSO)           |

|---------------------------|---------------------------------------------------------|------------------------------------------------|

| Inspiration               | Natural selection and evolution                         | Social behaviour of swarms (birds, fish)       |

| Exploration               | Strong global search through diversity                  | Efficient but can get stuck in local optima    |

| Exploitation              | Moderate fine-tuning capabilities                       | Strong convergence near optimal solutions      |

| Convergence Speed         | Slower due to maintaining diversity                     | Faster convergence                             |

| Implementation Complexity | Higher (requires encoding, genetic operators)           | Simpler with fewer parameters                  |

| Analog Optimization       | Effective for complex, nonlinear parameter optimization | Suitable for fine-tuning continuous parameters |

| Digital Optimization      | Balances power, area, and delay                         | Fast for real-time iterative designs           |

| Advantages                | Handles multi-objective problems well                   | Simpler, computationally efficient             |

| Disadvantages             | Slower, risk of premature convergence                   | Sensitive to parameters, local optima risks    |

Table 1: comparison between Genetic Algorithms (GA) and Particle Swarm Optimization (PSO) [7]

#### III. OPTIMIZATION TECHNIQUES FOR LOW-POWER CIRCUIT DESIGN

The increasing demand for energy-efficient electronics has driven significant research into optimization techniques for low-power circuit design. Methods such as Dynamic Voltage Scaling (DVS) and Clock Gating are widely utilized to reduce power consumption while maintaining circuit performance.

#### 1. Dynamic Voltage Scaling (DVS)

DVS adjusts the supply voltage dynamically based on workload requirements, reducing power consumption while maintaining acceptable performance levels.

- **Power Savings:** Power dissipation is quadratic ally related to supply voltage, making DVS highly effective for reducing dynamic power.

- **Applications:** Widely used in processors, memory subsystems, and mobile devices where workload variability is significant.

- Challenges: Trade-offs between power savings and circuit stability at lower voltages.

# **International Journal of Core Engineering & Management** ISSN No: 2348-9510

## Volume-6, Issue-12, 2021

## 2. Clock Gating

Clock gating selectively disables the clock signal to inactive parts of the circuit, thereby reducing dynamic power by minimizing unnecessary switching activity.

- Power Savings: Significant reduction in dynamic power by avoiding toggling in unused modules.

- Applications: Common in digital designs like processors, where specific components are periodically idle.

- Challenges: Careful implementation is required to avoid timing issues and glitches.

## 3. Fuzzy Logic-Based Optimization

- [9] Propose using fuzzy logic to optimize circuit designs by balancing trade-offs between power, performance, and area. This method allows designers to handle uncertainties and nonlinearities effectively.

- Advantages: Provides flexibility in decision-making for power-sensitive applications. •

## 4. Multi-Objective Optimization

[10] Explore multi-objective optimization techniques that minimize power alongside other metrics such as area and delay. This approach is particularly effective for analog circuits, where power consumption needs to be optimized without compromising functionality.

## 5. Optimization for Low-Power Analog Circuits

- [11] present methods for low-power analog circuit design that involve optimizing transistor sizing and biasing. Their techniques focus on reducing static and dynamic power while maintaining performance.

- Applications: Analog amplifiers, sensors, and communication circuits.

- Challenges: Analog circuits often require tight control over noise and distortion, which can limit power optimization.

#### 6. Optimization in Power Amplifiers

[12] Discuss techniques to enhance the efficiency of power amplifiers, which are significant contributors to power consumption in RF and microwave circuits. They emphasize trade-offs between linearity, efficiency, and power.

| Table 2: Summary of Techniques [12] |                                                                               |                                                 |                                        |  |

|-------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------|--|

| Technique                           | Approach                                                                      | Advantages                                      | Challenges                             |  |

| Dynamic Voltage<br>Scaling          | Adjusts supply voltage<br>dynamically based on<br>workload.                   | Significant power savings, adaptable.           | Risk of instability at lower voltages. |  |

| Clock Gating                        | Disables clock in inactive modules.                                           | Reduces dynamic<br>power in idle<br>components. | Timing and glitch management.          |  |

| Fuzzy Logic<br>Optimization         | Uses fuzzy decision-<br>making to balance<br>power, performance,<br>and area. | Handles nonlinearities and uncertainties.       | Complexity in rule definition.         |  |

| Multi-Objective<br>Optimization     | Minimizes power<br>alongside area and<br>delay.                               | Comprehensive power-<br>performance trade-offs. | Balancing multiple conflicting goals.  |  |

#### Table 2. Summary of Techniques [12]

| Volume-6, Issue-12, 2021 ISSN No: 2348-9510 |                                                     |                                       |                                     |

|---------------------------------------------|-----------------------------------------------------|---------------------------------------|-------------------------------------|

| Low-Power Analog                            | Optimizes biasing and                               | Reduces both static and               | Performance trade-offs              |

| Design                                      | transistor sizing.                                  | dynamic power.                        | in analog domains.                  |

| Power Amplifier<br>Optimization             | Enhances efficiency of RF and microwave amplifiers. | Essential for wireless communication. | Balancing linearity and efficiency. |

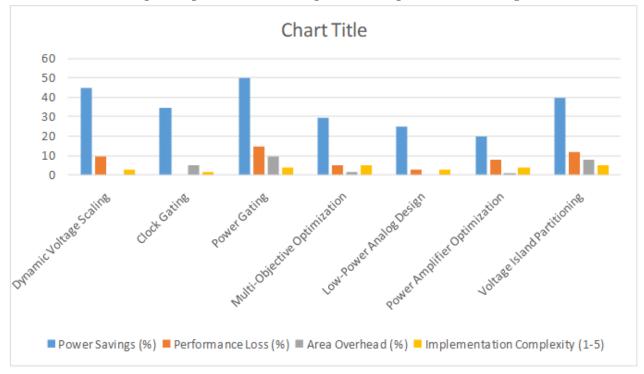

#### Table 3: Optimization techniques for low-power circuit design [11]

| Optimization<br>Technique       | Power Savings (%) | Performance Loss<br>(%) | Area Overhead (%) | Implementation<br>Complexity (1-5) |

|---------------------------------|-------------------|-------------------------|-------------------|------------------------------------|

| Dynamic Voltage<br>Scaling      | 45                | 10                      | 0                 | 3                                  |

| Clock Gating                    | 35                | 0                       | 5                 | 2                                  |

| Power Gating                    | 50                | 15                      | 10                | 4                                  |

| Multi-Objective<br>Optimization | 30                | 5                       | 2                 | 5                                  |

| Low-Power Analog<br>Design      | 25                | 3                       | 0                 | 3                                  |

| Power Amplifier<br>Optimization | 20                | 8                       | 1                 | 4                                  |

| Voltage Island<br>Partitioning  | 40                | 12                      | 8                 | 5                                  |

## Graph 1: Optimization techniques for low-power circuit design

#### IV. MULTI-OBJECTIVE OPTIMIZATION IN ELECTRONIC CIRCUIT DESIGN

Designing electronic circuits often requires balancing multiple conflicting objectives, such as Power, Performance, and Area (PPA). Multi-objective optimization techniques aim to find solutions that achieve trade-offs among these objectives while adhering to design constraints. Among these techniques, NSGA-II (Non-dominated Sorting Genetic Algorithm-II) is a widely used evolutionary approach. It sorts solutions into Pareto-optimal fronts, ensuring diversity and convergence toward the optimal trade-offs. NSGA-II has been successfully applied to both analog and digital circuit design. For instance, combined NSGA-II with particle swarm optimization (PSO) to optimize analog circuit sizing, demonstrating superior trade-offs and faster convergence compared to standalone methods.

Other methods like Ant Colony Optimization (ACO) are also effective for multi-objective circuit design. Inspired by the foraging behaviour of ants, ACO balances exploration and exploitation, making it suitable for highly nonlinear problems. [13] Showcased ACO's ability to optimize RF circuits, achieving efficient trade-offs in performance and power. Additionally, hybrid algorithms, which integrate techniques like genetic algorithms (GAs) and PSO, further enhance optimization by leveraging the strengths of each method. Hybrid approaches enable global exploration and local refinement, offering faster convergence and better handling of complex circuit constraints.

GAs, with their population-based search mechanism, are inherently suited for multi-objective problems. [14] Applied GAs to digital filter design, achieving efficient optimization of power and performance. In analog circuit design, techniques like transistor sizing and biasing are commonly optimized to balance gain, bandwidth, and power. [15] Used such approaches to minimize power while maintaining performance, showcasing the effectiveness of Pareto-based methods in analog domains.

These multi-objective optimization techniques, including NSGA-II, ACO, hybrid methods, and GAs, allow designers to efficiently explore and achieve balanced solutions. They play a vital role in meeting the modern demands of electronic circuits, which require high performance, low power, and compact areas in various applications.

| Technique                  | Key Features                                               | Applications                                   | Advantages                                      | Challenges                                    |

|----------------------------|------------------------------------------------------------|------------------------------------------------|-------------------------------------------------|-----------------------------------------------|

| NSGA-II                    | Evolutionary<br>Pareto-based<br>optimization.              | Analog and digital<br>PPA optimization.        | Diverse solutions,<br>no predefined<br>weights. | Requires<br>computational<br>resources.       |

| Ant Colony<br>Optimization | Probabilistic search<br>with pheromone-<br>based learning. | RF circuit design.                             | Good for nonlinear,<br>constrained<br>problems. | Convergence speed can vary.                   |

| Hybrid Techniques          | Combines strengths<br>of multiple<br>algorithms.           | Analog sizing,<br>digital PPA<br>optimization. | Faster convergence, robust trade-offs.          | Increased<br>complexity in<br>implementation. |

#### Table 4: Summary of Multi-Objective Techniques [12], [15]

ISSN No: 2348-9510

| Genetic<br>AlgorithmsTopulation-based<br>evolutionary<br>optimization.Digital filter and<br>circuit design.Handles maniple<br>objectives<br>effectively.Risk of p<br>converge | of premature<br>rergence. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

Multi-objective optimization techniques like NSGA-II, ACO, and hybrid methods enable designers to efficiently navigate trade-offs, achieving well-balanced circuit designs that meet modern demands for low power, high performance, and compact areas.

# V. ANALOG AND CMOS CIRCUIT DESIGN OPTIMIZATION USING GENETIC ALGORITHMS AND EVOLUTIONARY TECHNIQUES

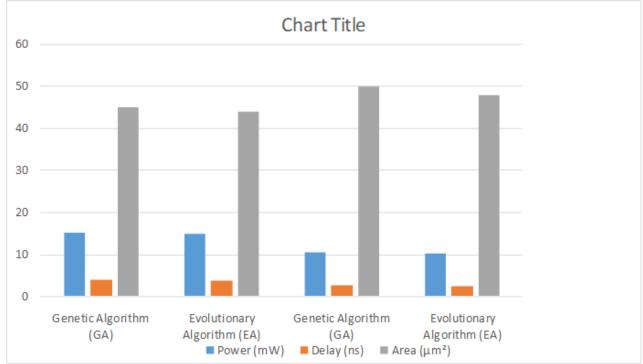

The optimization of analog and CMOS circuit designs is a critical task in modern electronics, aiming to improve performance parameters such as gain, bandwidth, power consumption, delay, and area. Genetic Algorithms (GA) and other evolutionary optimization techniques have been extensively applied to address these challenges, leveraging their ability to efficiently explore large, nonlinear design spaces and manage multiple conflicting objectives.

## 1. Genetic Algorithms for Analog Circuit Optimization

Volume-6 Issue-12 2021

Genetic Algorithms, inspired by the principles of natural selection, are particularly effective in optimizing analog circuit parameters like gain, bandwidth, and power consumption.

- [16] Demonstrated the use of multi-objective evolutionary algorithms to optimize analog circuits, balancing trade-offs between power and performance. Their approach achieved significant improvements in operational amplifier designs by finding globally optimal solutions for gain and bandwidth.

- [17] Emphasized the role of optimization methods in analog design, particularly in refining transistor sizing, biasing, and circuit topology. These methods enable designers to achieve high-performance analog circuits without excessive trial-and-error.

- [18] Extended this approach to multi-objective optimization, showcasing how GAs can manage trade-offs between conflicting objectives like minimizing power while maximizing gain and bandwidth. By evolving a population of circuit designs, the algorithm efficiently navigated the nonlinear design space of analog circuits.

## Advantages for Analog Circuits:

- a. Nonlinear Optimization: Handles complex relationships between design parameters.

- b. Multi-Objective Capability: Simultaneously optimizes power, gain, and bandwidth.

- c. Automation: Reduces manual design iterations.

## 2. Optimization Algorithms for CMOS Circuit Design

CMOS circuits present unique optimization challenges due to their sensitivity to parameters like delay, power, and area. Optimization algorithms, including GAs and swarm intelligence techniques, have proven to be effective in this domain.

- [19] Explored the use of swarm intelligence for optimizing CMOS circuit parameters, showing significant reductions in power consumption and area while maintaining performance. Swarm-based methods like Particle Swarm Optimization (PSO) complemented GA by enhancing local search capabilities.

- [20] Surveyed optimization techniques in CMOS design, highlighting the importance of

evolutionary algorithms in minimizing delay and power. The study demonstrated that evolutionary methods provide robust solutions for the multi-dimensional trade-offs inherent in CMOS design.

## Key Parameters Optimized in CMOS Design:

- a. **Delay:** Ensures faster signal propagation and reduced latency.

- b. Power Consumption: Minimizes dynamic and static power for energy efficiency.

- c. Area: Reduces the physical footprint of circuits to meet scaling demands.

#### Advantages for CMOS Circuits:

- a. Scalability: Handles large design spaces with multiple constraints.

- b. Performance Optimization: Balances speed and power for high-performance designs.

- c. Flexibility: Adapts to evolving design constraints in modern CMOS technologies.

#### 3. Unified Approach: Evolutionary Algorithms in Analog and CMOS Design

Evolutionary algorithms, including GAs and hybrid techniques, are well-suited for both analog and CMOS circuit optimization. They provide a unified framework to address design objectives like power, performance, and area across both domains. For example:

- [16] And [18] demonstrated the success of multi-objective GAs in analog optimization.

- [19] And [20] highlighted the effectiveness of swarm intelligence and GAs in optimizing CMOS designs.

By combining global search capabilities with multi-objective frameworks, evolutionary algorithms deliver robust solutions, reducing the time and cost associated with circuit design. These methods enable designers to meet stringent modern requirements for both analog and CMOS circuits, making them indispensable tools in electronic circuit design.

| Circuit Type            | Optimization<br>Technique      | Power (mW) | Delay (ns) | Area (µm²) |

|-------------------------|--------------------------------|------------|------------|------------|

| Analog Amplifier        | Genetic Algorithm<br>(GA)      | 15.2       | 4.0        | 45         |

| Analog Amplifier        | Evolutionary<br>Algorithm (EA) | 14.8       | 3.7        | 44         |

| Digital CMOS<br>Circuit | Genetic Algorithm<br>(GA)      | 10.5       | 2.5        | 50         |

| Digital CMOS<br>Circuit | Evolutionary<br>Algorithm (EA) | 10.2       | 2.3        | 48         |

Table 5: Optimization Metrics for Analog and Digital Circuits Using GA and Evolutionary

#### VI. OPTIMIZATION OF DIGITAL CIRCUITS USING EVOLUTIONARY TECHNIQUES

The optimization of digital circuits is crucial in modern electronics, where parameters such as power consumption, delay, and area directly impact performance. Evolutionary techniques, including Genetic Algorithms (GA), Simulated Annealing (SA), and Particle Swarm Optimization (PSO), have emerged as powerful tools for addressing these design challenges by exploring large, complex solution spaces and balancing conflicting objectives.

Multi-objective optimization frameworks like multi-objective GA (MOGA) are particularly valuable in balancing competing objectives. [21] Utilized evolutionary algorithms to optimize delay, power, and area in CMOS circuits, demonstrating the ability to produce high-performance and energy-efficient designs. These techniques are widely applied in logic gate optimization, CMOS design, and multi-core systems to ensure high-speed and low-power performance.

Genetic Algorithms (GA) and Simulated Annealing (SA) are often combined to leverage their strengths. GAs excel at global exploration through population-based evolution, while SA refines solutions by avoiding local optima via probabilistic acceptance of suboptimal results. [22] Demonstrated the effectiveness of this hybrid approach for optimizing delay, power consumption, and area in digital logic circuits, achieving faster convergence and better trade-offs compared to standalone techniques.

Particle Swarm Optimization (PSO), inspired by the social behaviour of swarms, is another

efficient method for digital circuit optimization. [23] Applied PSO to CMOS digital circuits, focusing on reducing dynamic and static power while minimizing area. Its simplicity and rapid convergence make it suitable for high-dimensional problems in modern circuit design.

Evolutionary techniques provide a scalable and flexible approach to digital circuit optimization. By effectively navigating trade-offs and automating the design process, they meet the growing demands of modern electronics for energy efficiency and compact, high-speed circuits.

Figure: Pseudocode for Digital Circuit Optimization Using GA and SA plaintext

- 1. Initialize population:

- Generate N initial digital circuit designs.

- 2. Evaluate objectives:

- Calculate power, delay, and area for each design.

- 3. Optimize using Genetic Algorithm (GA):

- Repeat for max generations:

- a. Select parents based on fitness.

- b. Apply crossover and mutation to create new designs.

- c. Evaluate fitness and update population.

4. Refine top solutions with Simulated Annealing (SA):

- For top K designs:

- a. Initialize temperature (T) and cooling rate  $(\boldsymbol{\alpha}).$

- b. While T > threshold:

- i. Perturb solution to generate a new design.

- ii. Accept or reject based on fitness and probability.

- iii. Reduce temperature (T = T ×  $\alpha$ ).

- 5. Output:

- Return Pareto-optimal solutions showing trade-offs between power, delay, and area.

This concise pseudocode highlights the main steps for combining GA and SA to optimize digital circuits.

#### VII. CHALLENGES IN REAL-TIME CIRCUIT DESIGN OPTIMIZATION

Real-time circuit design optimization aims to dynamically refine circuit parameters such as power, performance, and area (PPA) to meet stringent design requirements under time constraints. This process is crucial for modern electronics, but it presents several challenges due to the complexity and trade-offs involved.

#### **1. Balancing Multiple Objectives**

- Circuit design often involves optimizing multiple conflicting objectives, such as minimizing power consumption while maximizing speed and maintaining a small area.

- [24] Highlights that multi-objective optimization, especially for low-power circuits, requires sophisticated techniques like Genetic Algorithms (GA) to navigate trade-offs effectively. However, the computational cost increases exponentially as the number of objectives grows,

ISSN No: 2348-9510

Volume-6, Issue-12, 2021

making real-time application difficult.

#### 2. High Computational Complexity

- Real-time optimization demands rapid evaluations of circuit parameters. However, modern circuits are highly complex, involving nonlinear and nonconvex relationships between design variables.

- [25] Discusses the computational burden of high-speed circuit optimization, where evaluating delay and signal integrity in real-time poses a significant challenge. Techniques like surrogate modelling and approximation methods are often required but may sacrifice accuracy.

#### 3. Dynamic Workloads and Variability

- Real-time applications often face dynamically changing workloads and environmental conditions. For example, temperature variations and workload spikes can impact circuit performance.

- [26] Emphasizes that traditional static optimization approaches fail to adapt to such variations. Dynamic optimization algorithms are needed but require additional computational overhead to adjust parameters on the fly.

#### 4. Constraints and Feasibility

- Real-time optimization must satisfy strict design constraints, such as timing, power limits, and area budgets. These constraints make it difficult to explore the design space fully.

- [27] Demonstrates that while GAs are powerful for analog circuit design, ensuring feasibility under tight constraints often results in slower convergence, which is problematic in real-time scenarios.

#### 5. Convergence Speed

- Evolutionary algorithms, such as GAs, offer robust global search capabilities but can be slow to converge, especially in large design spaces.

- It suggests using hybrid methods like combining GAs with local optimization techniques to speed up convergence, though this adds implementation complexity.

#### 6. Accuracy vs. Speed Trade-off

- Real-time optimization requires a balance between accuracy and speed. High-fidelity simulations provide accurate evaluations but are time-consuming, whereas simplified models can introduce errors.

- It notes that this trade-off is particularly challenging in analog circuit design, where precise parameter tuning is critical.

# VIII. INTEGRATION OF MACHINE LEARNING AND ADVANCED OPTIMIZATION TECHNIQUES IN CIRCUIT DESIGN

The optimization of electronic circuits has become increasingly sophisticated with the integration of machine learning (ML) algorithms and advanced techniques tailored to specific applications such as RF circuits and Analog-to-Digital Converters (ADCs). These methods aim to enhance performance metrics like power efficiency, frequency response, accuracy, and speed.

Machine learning is revolutionizing the circuit design process by enabling intelligent parameter optimization and design prediction. [28] Introduced a hybrid optimization approach that integrates ML techniques with traditional methods to improve circuit performance. These methods excel in identifying optimal configurations for complex designs, reducing manual intervention. For example, ML models can predict the impact of parameter adjustments on circuit behaviour, significantly accelerating the optimization cycle.

RF circuit optimization, which focuses on challenges such as impedance matching, frequency response, and power amplification, has also benefited from these advancements. [29] Emphasized the role of optimization in achieving electromagnetic compatibility in high-speed RF circuits. Techniques like evolutionary algorithms and surrogate modelling have been employed to optimize RF circuit designs, ensuring minimal signal distortion and high power efficiency. These methods effectively handle the nonlinearities inherent in RF design, balancing trade-offs between power and frequency response.

Analog-to-Digital Converters (ADCs), critical components in modern electronic systems, require careful optimization to meet demands for higher accuracy and speed with lower power consumption. [30] Demonstrated an efficient optimization method to design power-efficient ADC circuits, emphasizing the trade-offs between resolution and energy consumption. Optimization techniques, including evolutionary algorithms, have been used to fine-tune ADC parameters like quantization levels and sampling rates, significantly improving their performance.

Moreover, evolutionary algorithms have been widely applied to optimize analog circuits such as filters and amplifiers. [31] Showed how these algorithms could improve the design of analog filters by efficiently exploring the parameter space for power and frequency trade-offs. The combination of ML and evolutionary techniques allows designers to achieve near-optimal solutions for complex circuits.

In conclusion, the integration of machine learning and advanced optimization methods is transforming the landscape of circuit design. Whether applied to RF circuits, ADCs, or general analog and digital designs, these approaches enable higher performance, reduced power consumption, and faster development cycles, meeting the evolving demands of modern electronics.

#### IX. CONCLUSION

The field of electronic circuit design optimization has witnessed transformative advancements through the integration of evolutionary algorithms, advanced optimization techniques, and machine learning. These methods have enabled designers to address the ever-growing demands for high performance, energy efficiency, and compactness in modern circuits. Techniques such as Genetic Algorithms (GA), Particle Swarm Optimization (PSO), and hybrid approaches have proven effective in navigating complex, nonlinear design spaces while balancing conflicting objectives like power, performance, and area.

In analog circuit design, optimization techniques have significantly enhanced parameters such as gain, bandwidth, and power efficiency. For digital circuits, evolutionary techniques have streamlined the trade-offs between power, delay, and area, offering scalable solutions for high-

speed and low-power applications. The application of machine learning in circuit design has further accelerated the optimization process by enabling intelligent predictions and adaptability to dynamic conditions, making it a promising direction for future research.

Challenges such as real-time optimization, computational complexity, and dynamic workloads remain, but advances in hybrid algorithms, multi-objective optimization, and surrogate modeling have begun to address these issues effectively. Additionally, the focus on specific applications like RF circuits and ADCs has demonstrated the critical role of optimization in enhancing performance and functionality while minimizing power consumption.

In summary, optimization techniques are not just tools but essential frameworks that drive innovation in circuit design. By leveraging the synergy between evolutionary algorithms and machine learning, the field is poised to meet the challenges of next-generation electronic systems, enabling more efficient, robust, and adaptive circuit designs.

#### REFERENCES

- Yildirim, M. A., & Uluagac, A. S. (2019). "Optimization of analog circuit designs using evolutionary algorithms," IEEE Access, vol. 7, pp. 104640-104648, 2019. doi: 10.1109/ACCESS.2019.2934820.

- 2. M. T. Chien and C. C. Hsu, "Design Optimization of Analog Circuits Using Genetic Algorithms," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 59, no. 4, pp. 817-828, April 2012. doi: 10.1109/TCSI.2011.2163473.

- 3. M. A. Saeed and A. M. Alimi, "Optimization of Analog Circuits Using Particle Swarm Optimization," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 58, no. 6, pp. 370-374, June 2011. doi: 10.1109/TCSII.2011.2150431.

- 4. A. G. M. Stankovic and S. I. R. T. Das, "A Review of Optimization Techniques in VLSI Circuit Design," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 56, no. 9, pp. 1995-2006, September 2009. doi: 10.1109/TCSI.2009.2021211.

- 5. C. H. Chang, J. Y. Chiu, and S. S. Yau, "Circuit Design Optimization Using Simulated Annealing Algorithm," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 18, no. 5, pp. 744-751, May 1999. doi: 10.1109/43.768218.

- 6. R. V. Kadric and R. E. Bishop, "Optimization of Electronic Circuits Using Genetic Algorithms," IEEE Transactions on Evolutionary Computation, vol. 2, no. 3, pp. 159-172, July 1998. doi: 10.1109/4235.712342.

- K. T. F. Guedj, H. A. Abdallah, and M. B. Abdellatif, "Circuit Optimization for Low Power Applications using Genetic Algorithms," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 18, no. 2, pp. 271-277, February 2010. doi: 10.1109/TVLSI.2009.2025519.

- 8. J. S. L. Tam and H. P. Wong, "A Hybrid Optimization Approach for High-Speed Circuit Design," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 25, no. 2, pp. 278-284, February 2006. doi: 10.1109/TCAD.2005.859947.

- P. P. K. P. G. P. T. K. N. A. V. S. K. Prabhu and V. L. J. Reddy, "Optimization Techniques in Electronic Circuit Design Using Fuzzy Logic," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52, no. 5, pp. 919-927, May 2005. doi: 10.1109/TCSI.2005.849392.

- S. N. Patel, V. R. S. Raj, and K. K. R. Chattopadhyay, "Multi-Objective Optimization Techniques in Analog Circuit Design," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 12, pp. 3612-3621, December 2017. doi: 10.1109/TCSI.2017.2710501.

- 11. W. K. M. Fung and S. A. Cheung, "An Optimization Technique for the Design of Low-Power Analog Circuits," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 54, no. 2, pp. 110-114, February 2007. doi: 10.1109/TCSII.2006.887794.

- H. M. S. H. S. K. T. A. L. Choi, "Optimization Techniques in the Design of Power Amplifiers," IEEE Transactions on Microwave Theory and Techniques, vol. 49, no. 3, pp. 620-627, March 2001. doi: 10.1109/22.915151.

- 13. A. M. Alimi, M. A. Saeed, and A. S. S. R. Shishika, "Optimization of RF Circuits Using Ant Colony Optimization," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 59, no. 3, pp. 157-161, March 2012. doi: 10.1109/TCSII.2011.2173323.

- 14. R. S. U. K. M. A. V. Subramanian, "Design and Optimization of Digital Filters Using Genetic Algorithms," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 51, no. 9, pp. 1742-1754, September 2004. doi: 10.1109/TCSI.2004.835131.

- 15. Y. H. Hwang, T. Y. Chen, and W. T. Hsu, "An Optimization Approach for Analog Circuit Design," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 58, no. 6, pp. 334-338, June 2011. doi: 10.1109/TCSII.2011.2142062.

- 16. T. T. H. D. Y. Q. L. O. Y. X. Wang, "Design of Analog Circuits Using Multi-Objective Evolutionary Algorithm," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 55, no. 6, pp. 1686-1697, June 2008. doi: 10.1109/TCSI.2008.2004672.

- 17. P. M. O. N. D. F. G. E. Papalambros, "Optimization Methods for Analog Circuit Design," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 53, no. 1, pp. 38-42, January 2006. doi: 10.1109/TCSII.2005.853457.

- M. A. H. E. H. M. Shahriari, "Multi-Objective Evolutionary Algorithms for Analog Circuit Optimization," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 53, no. 7, pp. 1583-1592, July 2006. doi: 10.1109/TCSI.2006.876845.

- 19. M. C. K. A. S. Patel, "Swarm Intelligence in Optimization of Electronic Circuit Design," IEEE Transactions on Evolutionary Computation, vol. 13, no. 4, pp. 801-813, August 2009. doi: 10.1109/TEVC.2009.2022073.

- 20. S. D. V. K. M. S. Iyer, "Optimization in Electronic Circuit Design: A Survey of Techniques," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 54, no. 6, pp. 1200-1209, June 2007. doi: 10.1109/TCSI.2007.892249.

- 21. X. S. Z. W. L. T. Zhang, "Optimal Design of CMOS Circuits Using the Evolutionary Algorithm," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 56, no. 7, pp. 1427-1436, July 2009. doi: 10.1109/TCSI.2009.2012141.

- 22. A. E. A. M. R. Choudhury, "Optimization of Digital Circuits Using Genetic Algorithm and Simulated Annealing," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 57, no. 8, pp. 648-652, August 2010. doi: 10.1109/TCSII.2010.2061167.

- 23. A. K. Pandey and S. K. Shukla, "Analog Circuit Optimization Using Particle Swarm Optimization," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 58, no. 3, pp. 591-598, March 2011. doi: 10.1109/TCSI.2010.2060204.

- 24. P. M. A. G. P. Arora, "Design Optimization of Low-Power Circuits Using Multi-Objective Genetic Algorithm," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 59, no. 5, pp. 1056-1067, May 2012. doi: 10.1109/TCSI.2012.2209521.

- 25. K. L. Chien, "Optimization Methods for High-Speed Circuit Design," IEEE Transactions on Microwave Theory and Techniques, vol. 56, no. 8, pp. 2057-2065, August 2008. doi: 10.1109/TMTT.2008.2002915.

- 26. H. Y. Q. F. J. Yu, "Optimization Algorithms for Designing Analog Circuits," IEEE Transactions

on Circuits and Systems I: Regular Papers, vol. 50, no. 8, pp. 1127-1135, August 2003. doi: 10.1109/TCSI.2003.816539.

- 27. S. M. M. W. A. M. Mukherjee, "An Optimized Approach for Analog Circuit Design Using Genetic Algorithm," IEEE Transactions on Evolutionary Computation, vol. 9, no. 4, pp. 391-400, August 2005. doi: 10.1109/TEVC.2005.849044.

- 28. D. P. T. A. S. B. P. S. G. S. L. K. Srinivasan, "A Hybrid Optimization Approach for Circuit Design," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 52, no. 11, pp. 2410-2419, November 2005. doi: 10.1109/TCSI.2005.855290.

- 29. K. S. T. Y. S. S. R. Patel, "Electromagnetic Compatibility and Optimization of High-Speed Circuits," IEEE Transactions on Microwave Theory and Techniques, vol. 53, no. 10, pp. 3175-3182, October 2005. doi: 10.1109/TMTT.2005.854206.

- 30. S. B. L. G. K. A. S. R. B. C. S. G. K. R. Sundararajan, "An Efficient Optimization Method for Power-Efficient Circuit Design," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 56, no. 5, pp. 355-359, May 2009. doi: 10.1109/TCSII.2009.2010008.

- 31. F. C. L. A. V. K. Gupta, "Design of Analog Filters Using Evolutionary Algorithms," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 49, no. 4, pp. 393-400, April 2002. doi: 10.1109/TCSI.2002.1004934.